Table of Contents

Executive Summary

Co-Packaged Optics (CPO) represents a paradigm shift in data center and high-performance computing (HPC) infrastructure, moving optical engines directly alongside switch ASICs and processors to overcome the bandwidth and power limitations of traditional electrical I/O. Taiwan Semiconductor Manufacturing Company (TSMC) has positioned itself at the forefront of this revolution by successfully integrating its CPO technology with advanced packaging platforms like CoWoS and SoIC . For the PCB industry, this signals a fundamental transition. The role of the traditional PCB is evolving, demanding new expertise in high-frequency materials, advanced thermal management, and system-level co-design to support the next generation of AI-driven hardware.

1.The CPO Vision: Why Optics are Moving Closer to Silicon

The relentless growth of artificial intelligence and machine learning workloads is pushing data transmission rates to unprecedented levels. Traditional architectures, where separate pluggable optical modules are connected to switches and GPUs via PCB traces, are hitting a wall. At data rates of 800G and beyond, these copper-based electrical paths become major bottlenecks, consuming excessive power and suffering from signal integrity issues .

CPO technology addresses this by co-packaging the optical engine and the compute silicon (like a switch ASIC or GPU) on a common substrate or interposer. This dramatically shortens the electrical connection from several centimeters to a few millimeters, leading to:

•Significant Power Reduction: Eliminating long, lossy PCB traces and the need for powerful DSPs in pluggable modules can reduce link power consumption by 30-50% .

•Massive Bandwidth Density: CPO enables unprecedented I/O bandwidth, with implementations like TSMC’s COUPE platform targeting 1.6T and 6.4T optical engines .

•Overcoming Copper Limitations: By converting electrical signals to optical ones within the package, CPO bypasses the fundamental bandwidth-distance constraints of copper traces on PCBs .

2.TSMC’s CPO Technology Stack: A Multi-Dimensional Integration

TSMC’s strength lies not in creating a single component, but in its ability to integrate multiple advanced technologies into a single, cohesive solution. Its CPO strategy rests on three core pillars.

2.1 The Silicon Photonics Engine: MRMs and the COUPE Platform

At the heart of TSMC’s CPO solution is its silicon photonics technology, which allows for the fabrication of optical components on standard silicon wafers.

•Micro-Ring Modulator (MRM): TSMC, in collaboration with Broadcom and NVIDIA, has successfully qualified its key CPO technology—the MRM—on a 3nm process node . MRMs are tiny, resonant silicon rings that can modulate a laser beam to encode electrical data onto an optical signal. Their small size and low power consumption make them ideal for building dense, multi-channel optical I/O arrays. TSMC’s MRMs are designed to support 200 Gbps per channel using PAM4 modulation .

•The COUPE Platform: TSMC’s Compact Universal Photonic Engine (COUPE) is a comprehensive silicon photonics platform. It integrates the Photonic Integrated Circuit (PIC), containing components like MRMs and germanium photodetectors, with an Electronic Integrated Circuit (EIC) for control and driving functions . This platform provides a foundation for building the optical engines that will be co-packaged with ASICs.

2.2 Advanced Packaging: The Enabler of Co-Packaging

The true innovation is how TSMC brings the optical and electronic components together. The company is leveraging its industry-leading packaging technologies to achieve this.

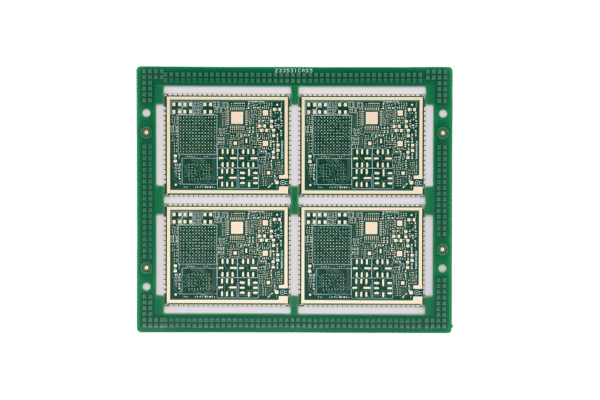

•Integration with CoWoS: TSMC’s primary path involves integrating the CPO module with its CoWoS (Chip-on-Wafer-on-Substrate) packaging platform . This allows a large compute chip and multiple optical engine chiplets to be mounted side-by-side on a silicon interposer, providing the dense, high-speed electrical connections between them.

•Future Direction with SoIC: For even tighter integration, TSMC is exploring the use of SoIC (System-on-Integrated-Chip), a 3D chip-stacking technology using direct hybrid bonding . This could eventually allow for the vertical stacking of photonic and electronic dies, creating an even more compact and efficient system.

2.3 The Path to Manufacturing: Timeline and Key Players

TSMC’s CPO technology is rapidly progressing from development to commercialization.

•Product Timeline: Development of key technologies like the MRM is complete . The industry can expect TSMC to deliver 1.6T CPO samples in 2025, with volume production ramping up in 2026 .

•Strategic Partnerships: This effort is highly collaborative. TSMC is working closely with key industry drivers like NVIDIA and Broadcom, who are expected to be the first major clients for its CPO solutions . NVIDIA’s own CPO platforms, such as the Quantum-X Photonics switch, already leverage TSMC-fabricated silicon photonics engines .

3.Implications for the PCB Industry: Evolution and Adaptation

The adoption of CPO does not make the PCB obsolete; instead, it fundamentally changes the PCB’s role and design requirements.

3.1 The Shift in PCB Functionality

With the highest-speed I/O moving inside the package, the main PCB’s function evolves from a high-speed data highway to a platform for:

•Power Delivery: Designing a robust Power Delivery Network (PDN) becomes even more critical to supply clean, stable power at high currents to advanced packages.

•Low-Speed Signaling and Control: Managing control interfaces, lower-speed I/Os, and peripheral connections.

•Thermal Management: The PCB must serve as an effective thermal management path, helping to dissipate the concentrated heat from co-packaged optics and ASICs.

3.2 New Design and Manufacturing Challenges for PCB Manufacturers

This shift presents several new challenges that PCB fabricators must address:

•Material Science: PCBs for CPO-based systems will require advanced, low-loss dielectric materials (e.g., Megtron 6/7/8) to support any remaining high-speed channels and power integrity. The thermal stability of these materials is also paramount.

•Thermal Management: The power density of these systems is immense. PCB designs must incorporate sophisticated cooling solutions, such as embedded heat spreaders, thermal vias, and possibly direct attachment to liquid cold plates.

•Increased Complexity and Layer Count: System-on-Package architectures may lead to PCBs with higher layer counts to accommodate complex power planes and a multitude of lower-speed signals, all while maintaining strict impedance control.

•Interfacing with the Package: The PCB must provide a reliable and high-density interconnect interface to the advanced package, which may involve using high-density interconnect (HDI) technology and advanced laminates to manage the coefficient of thermal expansion (CTE) mismatch between the package substrate and the PCB.

4.The Future Landscape: What’s Next for CPO and PCBs

TSMC’s roadmap for CPO extends beyond the initial 1.6T integration.

•Roadmap to Higher Bandwidth: The COUPE platform outlines a clear path to 6.4T optical engines for CPO and even 12.8T for Optical I/O in the future . This will continue to push the requirements for supporting infrastructure, including PCBs.

•Photonic Interconnect Fanout (PIFO): TSMC is already developing Photonic Interconnect Fanout (PIFO) technology, which uses ultra-low-loss silicon nitride waveguides to route optical signals across a chiplet-based system . This could further redistribute optical pathways, potentially influencing how optical signals are managed across a larger module or board.

•A Collaborative Ecosystem: The success of CPO relies on a tightly integrated ecosystem spanning semiconductor foundries, OSATs, connector manufacturers, and PCB fabricators. Close collaboration will be essential to solve system-level challenges in thermal, mechanical, and electrical design.

5.Conclusion

TSMC’s advancement in CPO integration marks a significant milestone in the evolution of computing hardware. By moving optics directly into the package, they are solving critical power and bandwidth challenges that threaten the progress of AI and HPC.

For the PCB industry, this is not a threat but a call to innovate. The transition to CPO-based systems will demand higher-performing PCB materials, more sophisticated thermal management strategies, and a deeper understanding of system-level co-design. Companies that can master these new requirements—providing advanced substrates that meet the thermal, mechanical, and signal integrity demands of co-packaged optics—will be vital partners in building the high-performance computing infrastructure of the future.

Partner with Us for the Future of High-Speed Design

The shift towards co-packaged optics presents new challenges and opportunities at the system level. Our expertise in advanced PCB manufacturing, thermal management solutions, and high-speed material selection can help you design and build the robust platforms required for next-generation CPO-based systems.

Contact us today to discuss how we can support your projects in this new architectural landscape.