Table of Contents

Understanding the Foundation of Modern Electronics

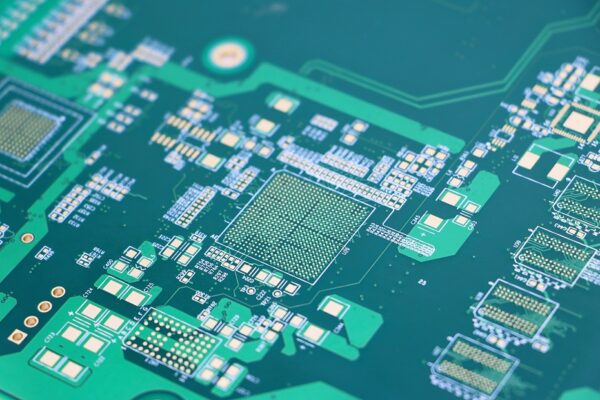

Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) are the fundamental building blocks of modern electronics. While both PMOS (P-channel MOSFET) and NMOS (N-channel MOSFET) regulate current flow using gate voltage, their structural differences create distinct advantages, limitations, and design requirements. For PCB engineers, understanding these differences is critical for optimizing power efficiency, thermal management, and signal integrity.

Core Structural Differences

| Characteristic | NMOS | PMOS |

| Substrate Material | P-type silicon | N-type silicon |

| Charge Carriers | Electrons (higher mobility) | Holes (lower mobility) |

| Turn-On Condition | Positive VGS (gate > source) | Negative VGS (gate < source) |

| Default State | Normally OFF | Normally ON* |

| Conduction Speed | 2–3× faster than PMOS | Slower switching |

| On-Resistance (RDS(on)) | Lower for same die size | Higher for same die size |

*PMOS requires negative bias to turn OFF

Performance Comparison: Critical Metrics

1.Electron Mobility Advantage

Electrons (NMOS) move 2.6× faster than holes (PMOS), enabling:

–Higher switching speeds (100+ MHz vs. 40 MHz)

–Lower conduction losses (RDS(on) reduced by 30–50%)

–Better efficiency in high-frequency circuits

2.Thermal Behavior

–NMOS: Lower heat generation at high currents due to reduced RDS(on)

–PMOS: Requires larger die sizes for equivalent current handling → increased parasitic capacitance

3.Noise Immunity

PMOS less susceptible to substrate noise in mixed-signal designs

Circuit Applications & Topologies

Where NMOS Excels

•Low-side switching (ground-referenced loads)

•High-speed digital logic (CPUs, memory)

•Buck converters (synchronous rectifiers)

•Motor drivers (efficient high-current paths)

Where PMOS Shines

•High-side switching (battery-connected loads)

•Load switches (simpler gate drive vs. NMOS bootstrap)

•Overvoltage protection (intrinsic body diode use)

•Input/output isolation in power management ICs

CMOS: The Ultimate Synergy

Complementary MOS (CMOS) combines PMOS and NMOS to eliminate static power consumption:

– PMOS pulls output to VDD

– NMOS pulls output to GND

– Near-zero quiescent current (nA range)

– Dominates 99% of modern ICs (microprocessors, FPGAs, sensors)

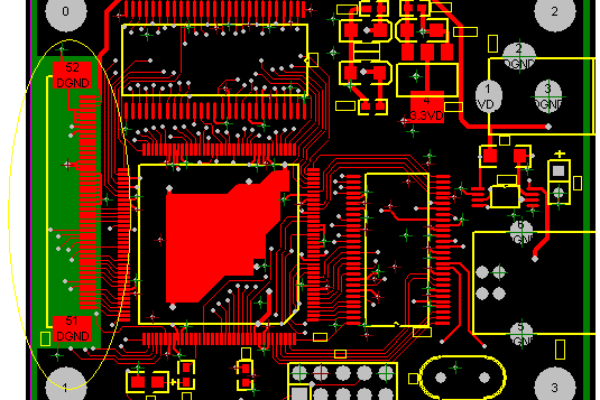

PCB Design Considerations

1. Gate Driving Challenges

| Parameter | NMOS | PMOS |

| Drive Voltage | VGS > Vth (e.g., +5V to +10V) | VGS < Vth (e.g., -5V to -10V) |

| High-Side Drive | Requires bootstrap circuit | Direct drive (gate ≤ source) |

| Solution | Dedicated gate driver ICs | Level-shifting circuits |

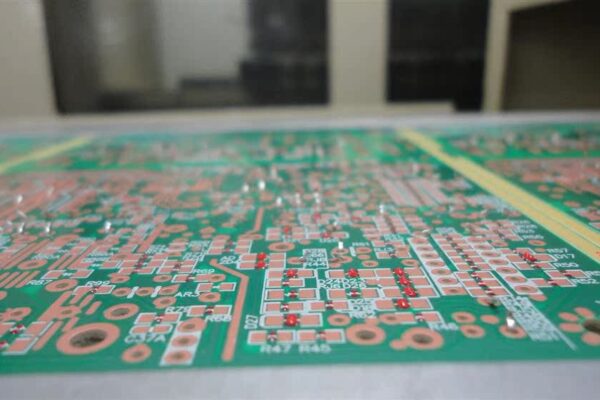

Layout Tip: Place gate resistors <5mm from MOSFET pins to reduce ringing.

2. Thermal Management

•NMOS: Use 2 oz copper pours + thermal vias under drain pins

•PMOS: Larger copper areas required due to higher RDS(on)

•Critical: Thermal relief pads ≠ electrical connections

3. Parasitic Effects

•Body Diode Reverse Recovery (Qrr):

NMOS diodes recover 30% faster than PMOS → lower losses in synchronous rectifiers

•Parasitic Capacitance (Ciss, Coss, Crss):

Impacts switching losses; model with SPICE pre-layout

Material & Stackup Recommendations

| Application | PCB Technology | Benefit |

| High-Power NMOS | Metal-Core PCBs (IMS) | 8× better heat dissipation vs. FR-4 |

| High-Frequency CMOS | Ultra-Low Loss Rogers 4350B | <0.0037 Df @ 10 GHz for GHz clocks |

| Space-Constrained | HDI with Via-in-Pad | Minimizes gate loop inductance |

| High-Voltage | 3.0mm Creepage (IEC 60950) | Prevents arcing in 600V systems |

SysPCB’s MOSFET-Optimized PCB Solutions

We ensure peak MOSFET performance through:

1.Signal Integrity First

–≤10% impedance tolerance for gate traces

–Guard rings to isolate sensitive gate drives

2.Thermal Superhighways

–Staggered Thermal Vias: 0.3mm diameter array under MOSFETs

–Embedded Copper Coins: Slash thermal resistance by 60%

3.Manufacturing Precision

–Laser-cut solder dams prevent bridging in <0.5mm pitch packages

–AOI for micro-shorts in CMOS IC fanouts

4.Reliability Validation

–Power cycling tests (50k cycles @ ΔT=80°C)

–TDR testing for gate signal reflections

Future Trends

•GaN/SiC Integration: Hybrid designs using NMOS-like GaN + PMOS silicon

•3D Packaging: PMOS/NMOS stacked vertically in advanced SoCs

•AEC-Q101 Qualified MOSFETs: Automotive-grade PCBs with 150°C capability

Conclusion: Choosing the Right MOSFET for Your Design

•Use NMOS when: Speed, efficiency, and low RDS(on) are critical (low-side switches, processors)

•Use PMOS when: Simplified high-side drive or negative voltage handling is needed

•Always prefer CMOS: For ultra-low-power digital logic

SysPCB delivers high-reliability PCBs engineered for demanding MOSFET applications:

-12-layer HDI for GHz-speed CMOS processors

-IMS substrates for 500W+ power stages

-IPC-6012 Class 3/AEC-Q200 compliance

Optimize your MOSFET circuits today!

→ [Request a free PCB design review]

→ [Download our “MOSFET Layout Checklist”]

→ [Explore our power electronics portfolio]