Table of Contents

The Critical Role of Via Finishes in PCB Reliability

Vias (plated through-holes) connect PCB layers, but their finishing treatment determines reliability, solderability, and signal integrity. Misunderstanding “Tenting,” “Plugging,” and “Exposed” vias causes 23% of DFM failures. Here’s how to specify them correctly:

Via Treatment Types: Definitions & Applications

| Term | Process | Visual | Best For | Avoid When |

| Tenting | Solder mask covers via hole & pad | ⬤ Green-covered | Cost-sensitive designs, signal vias | High-current/thermal vias |

| Plugging | Via filled with epoxy before mask coat | ⬤ Flat surface | BGA escape routes, HDI boards | High-frequency RF (>10 GHz) |

| Exposed | Solder mask removed from via pad | ⬤ Metallic ring | Thermal vias, test points | High-corrosion environments |

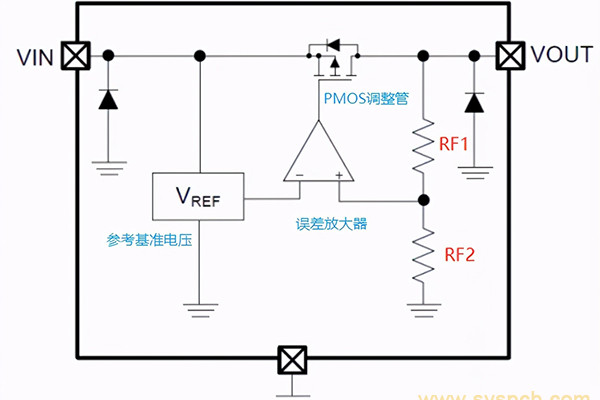

Why Your Choice Matters: Performance Implications

1.Solder Wicking Prevention (Critical for BGA)

- Plugged vias block solder migration → Reduce BGA voids by 40%

- Tented vias risk mask cracks → Solder wicks into hole during reflow

2.Thermal Management

- Exposed vias: Direct thermal path → 40% lower RθJA vs. tented

- Plugged vias: Thermal epoxy conducts heat 5× better than air

3.Signal Integrity

- Tenting: Prevents contamination in RF vias → <0.1dB loss @ 6GHz

- Plugging: Avoids impedance discontinuities in HDI microvias

4.Reliability Risks

Untreated via holes trap chemicals → CAF failure risk ↑300% in humid environment

How to Specify in Your Fabrication Notes

Clear Instructions Prevent Manufacturing Errors:

// EXAMPLE SPECIFICATION //

VIA TREATMENT:

– All vias under 0.3mm: PLUGGED (IPC-4761 Type VII)

– Thermal vias (PAD_THERM1-4): EXPOSED + Cu-filled

– Remaining vias: TENTED (solder mask over annular ring)

IPC Standards Reference:

– IPC-4761: Via protection types (Type I-VII)

– IPC-6012: Acceptability criteria for plugged vias

Responding to EQ (Engineering Query) Requests

Manufacturers issue EQs when via specs are unclear. Respond strategically:

EQ Scenario 1: “Via treatment not specified”

→ Your Response:

“Apply tenting for vias <0.5mm, plugging for vias under BGAs (components U1-U6), and expose thermal vias (pads marked ‘TH’). Refer to layer 28 drill file for via classifications.”

EQ Scenario 2: “Cannot plug vias below 0.2mm”

→ Your Response:

“Accept tenting with solder mask ink filling (IPC-4761 Type II) for vias <0.2mm. Ensure 100% mask coverage over annular rings.”

EQ Scenario 3: “Exposed vias may cause solder leakage”

→ Your Response:

“Add solder dam (0.07mm clearance) around exposed vias. Use LPISM-SR8 solder mask for reduced wicking risk.”

SysPCB’s Via Treatment Solutions

We ensure precision via finishing with:

1. Advanced Plugging Tech

– Laser-cleaned microvias (<0.15mm) → 99% void-free epoxy fill

– Capillary-flow fillers: Prevent dimples on plugged surfaces

2.DFM Optimization

- Auto-flag vias requiring plugging under BGAs/QFNs

- Impedance modeling for tented vs. exposed RF vias

3.Reliability Testing

- IST (Interconnect Stress Test): Validates plugged vias @ 150°C, 50 cycles

- CAF Resistance: 85°C/85% RH testing per IPC-TM-650

Cost & Lead Time Considerations

| Treatment | Cost Impact | Lead Time Add | Key Benefit |

| Tenting | None | None | Lowest cost |

| Plugging | +15–25% | 2–3 days | Prevents wicking, improves CAF |

| Exposed | +5% | 1 day | Optimal thermal dissipation |

Pro Tip: Use plugging only under BGAs and high-density areas to control costs.

Critical Design Rules for Each Treatment

1.Tenting

- Annular ring ≥ 0.05mm for mask adhesion

- Avoid on vias within 0.1mm of SMT pads

2.Plugging

- Via aspect ratio ≤ 8:1 (e.g., 0.2mm via depth max for 0.025mm hole)

- Specify fill material: Conductive epoxy (Ag-filled) or non-conductive

3.Exposed

- Add “SOLDER PASTE OPEN” in fab notes to prevent stencil coverage

- Use ENIG finish for oxidation resistance

Conclusion: Mastering Via Specs Prevents Failures

Choosing correct via treatments impacts manufacturing yield, field reliability, and electrical performance. Explicit specifications eliminate EQ delays and ensure optimal results.

[Your Company Name] delivers industry-leading via finishing:

– <0.1mm microvia plugging for 01005 BGAs

–Automated tenting validation via AOI

– Exposed via solder dams to IPC Class 3 standards

Optimize your via strategy today!

→ [Download our Via Treatment Design Guide]

→ [Request a free DFM review]

→ [Get your custom IPC-4761 specification sheet]