The design for manufacturability (DFM) of multi-layer PCBs requires consideration of performance, cost, and process compatibility, involving multiple dimensions such as stacking planning, layout and routing, and process adaptation. Here is a summary of key techniques:

Table of Contents

Ⅰ.Layered design: laying the foundation framework

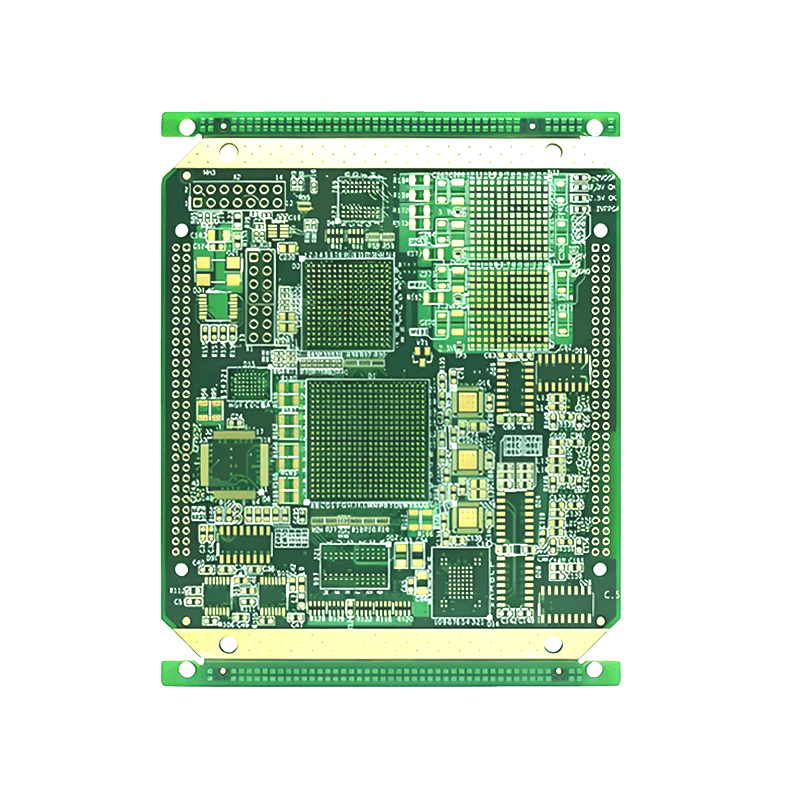

1. Functional layering principle

-The signal layer is prioritized to be close to the ground plane (GND), forming a “shielding cavity” using the ground plane to reduce electromagnetic interference (EMI); The high-speed signal layer (such as 100MHz and above) needs to be separately assigned a complete reference layer (ground or power plane) to avoid impedance jumps caused by cross layer references.

-The power layer (PWR) and ground layer (GND) should be as adjacent as possible to form a “planar capacitor” to reduce power noise (recommended spacing ≤ 0.2mm to enhance decoupling effect).

-Typical stacking example (4-layer board): Signal 1 → GND → PWR → Signal 2 (prioritize ensuring that the signal layer has a reference ground); The 8-layer board can add a middle signal layer, following the symmetrical structure of “signal ground signal power supply signal ground signal” to reduce board warping.

2. Impedance and layer spacing matching

-Confirm the substrate parameters (such as dielectric constant ε r) with the PCB factory in advance, and calculate the target impedance (such as 50 Ω single ended, 100 Ω differential) based on line width and layer spacing to ensure the impedance continuity of high-speed signals (such as USB 3.0, DDR).

-Control the distance between the signal layer and the reference layer (e.g. microstrip line ≤ 0.15mm, strip line ≤ 0.2mm) to avoid low impedance or signal attenuation caused by excessive layer spacing.

Ⅱ.Through hole design: balancing performance and process

1. Selection of through-hole types

-Through holes: Low cost, but can penetrate all layers and easily introduce parasitic inductance (≈ 0.5-2nH). High speed signals (>1GHz) should be used with caution; Suggest only for power/ground connections or low-speed signals.

-Blind/buried holes: Reduce interference with non target layers (such as BGA pin escape routing), but confirm the PCB factory’s process capability (the minimum aperture of laser blind holes can reach 0.1mm, which is costly).

2. Through hole size and process adaptation

-Aperture: The minimum diameter for mechanical drilling is ≥ 0.2mm (to avoid breakage), while laser drilling can reach up to 0.05mm, but it needs to match the plate thickness (aperture/plate thickness ≤ 0.15 to prevent poor copper plating on the hole wall).

-Solder pad: diameter ≥ aperture+0.2mm (e.g. 0.3mm aperture corresponds to 0.5mm solder pad), to prevent solder pad detachment; BGA area via holes need to be plugged and covered with oil to prevent solder from flowing into the holes and causing short circuits.

Ⅲ.Layout: Partition isolation and space reservation

1. Functional zoning and isolation

-Divided by signal type: analog area (ADC/DAC), digital area (MCU), high-frequency area (RF front-end), power area (DC-DC). Physically isolated to avoid interference from digital noise on analog signals (spacing ≥ 5mm, separated by grounding copper foil if necessary).

-Sensitive components (crystal oscillator, phase-locked loop) should be kept away from noise sources (switching power supply, relay), the crystal oscillator housing should be grounded, and the wiring length should be ≤ 10mm.

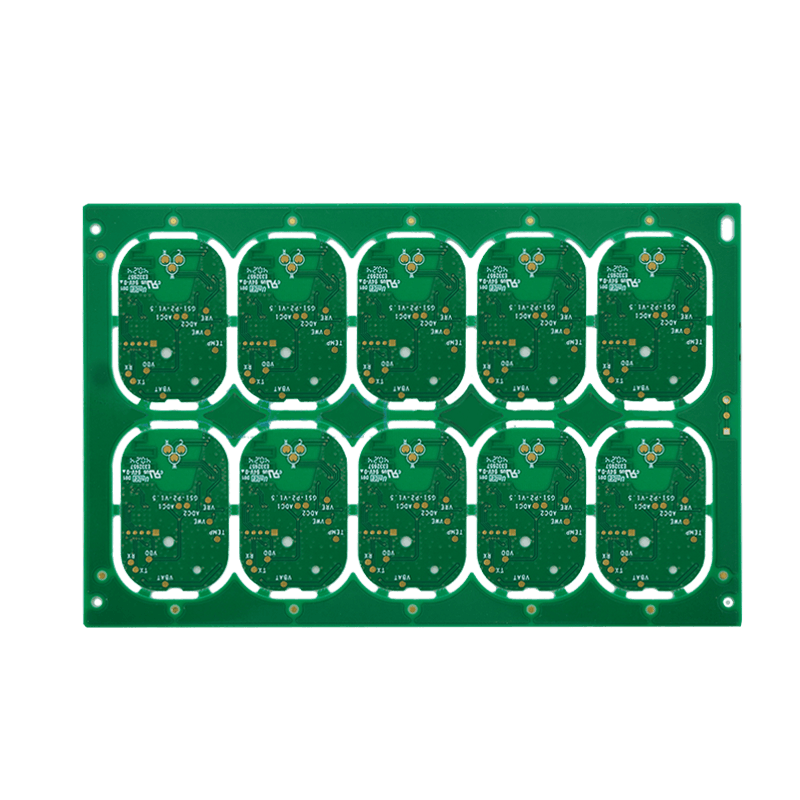

2. High density packaging layout

-Reserve a “fan out area” below BGA/QFP devices with fine pitch (pin spacing ≤ 0.8mm), and arrange the vias radially to avoid interference with surrounding components; Fan out wiring should be aligned with subsequent wiring directions (such as alternating horizontal/vertical) to reduce winding.

-Heavy components (transformers, large capacitors) are located near the edges or support points of the PCB to reduce the risk of warping after soldering; The distance between components with large height differences (such as connectors and chips) should be ≥ 2mm to avoid assembly interference.

Ⅳ.Wiring: Signal Integrity and Process Constraints

1. High speed signal priority

-Differential pairs (such as HDMI and Ethernet) should be of equal length (with an error of ≤ 5mil) and equidistant (maintaining coupling), avoiding through holes and right angles (using 45 ° angles or arcs), and impedance matching should be fine tuned through line width/spacing.

-The clock signal should follow a straight line to avoid branching, and the reference plane below should be continuous (without crossing the power supply). If necessary, it should be covered with ground shielding (the distance between the ground copper skin and the signal line should be ≥ 3 times the line width).

2. Power and ground wiring

-The line width of high current paths (such as DC-DC output) is calculated based on the current (1oz copper thickness: 1A corresponds to 1mm line width) to avoid bottlenecks; The power layer is divided into voltage zones (such as 3.3V/5V) and separated by an isolation tape of 0.5mm or more to prevent short circuits.

-The grounding copper foil needs to be “fully connected”, and the analog ground should be connected to the digital ground at a single point (such as through a 0 Ω resistor or magnetic beads) to avoid ground loop noise.

3. Process constraints

-Minimum line width/spacing: ordinary process ≥ 0.1mm (4mil), fine line process ≥ 0.075mm (3mil), to avoid etching and wire breakage; The power supply/layer copper skin needs to be equipped with “heat dissipation strips” (line width ≥ 0.5mm) to prevent uneven etching.

Ⅴ.Heat dissipation and reliability design

1. Heat dissipation enhancement

-A large area of copper foil is laid below the power devices (MOS tubes, power amplifiers), and connected to the inner ground/power plane through thermal vias (diameter 0.3-0.5mm, spacing 2-3mm) to enhance thermal conductivity.

-In areas with high heat flux density (such as CPUs), windows can be opened to expose copper (increase soldering volume), or reserved soldering positions for heat sinks (copper skin thickness ≥ 2oz).

2. Mechanical reliability

-Reserve a copper free area of ≥ 5mm at the edge of the board (for easy fixture fixation), and add positioning holes at the four corners (diameter 3-4mm, non-metallic).

-Large areas of copper foil require the addition of a “grid” (grid size 5-10mm) to avoid board warping or solder mask bubbles caused by thermal expansion and contraction.

Ⅵ.Process adaptation: docking with PCB factory specifications

-Obtain DFM documentation in advance: Confirm the maximum number of layers, minimum aperture/line width, board thickness range (such as conventional 0.8-3.2mm), copper thickness (1oz/2oz), and other process limits of the PCB factory to avoid design deviations (such as a minimum board thickness of 1.2mm for 6-layer boards).

-Test point reservation: Key signals (power supply, clock) are equipped with test points (diameter ≥ 0.8mm), located away from components, with a spacing of ≥ 1mm to facilitate probe contact.

Summarize

The core of DFM for multi-layer PCBs is “balance”: on the premise of meeting signal integrity and power integrity, it adapts to the PCB factory’s process capabilities through reasonable stacking, via, layout and wiring design, and ultimately achieves low-cost and high yield mass production. Before design, it is necessary to synchronize and standardize with PCB and assembly factories to reduce the cost of later modifications.

Get your exclusive quote immediately: fill out the form or send an email directly, and we will provide you with a quote service within 24 hours. Enjoy free DFM optimization and a 10% discount on SMT patches for your first order!