Table of Contents

1. Introduction: The Advanced Packaging Revolution

The exponential growth of AI, 5G, and high-performance computing (HPC) is driving unprecedented innovation in semiconductor packaging. CoWoS (Chip-on-Wafer-on-Substrate), CoPoS (Chip-on-Panel-on-Substrate), and CoWoP (Chip-on-Wafer-on-PCB) represent three evolutionary paths to overcome the limitations of traditional 2.5D/3D packaging. For PCB manufacturers, these technologies demand new capabilities in high-density interconnects (HDI), precision materials, and thermal management—positioning PCBs as critical performance enablers in the AI era .

2. Technology Breakdown: Core Architectures

2.1 CoWoS: The Incumbent Benchmark

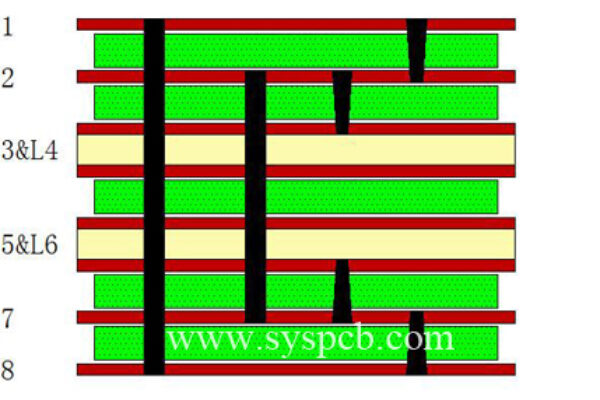

•Structure: Silicon interposer → ABF substrate → PCB .

•Key Types:

–CoWoS-S: Silicon interposer for HBM/GPU integration (e.g., NVIDIA H100).

–CoWoS-R: Redistribution Layer (RDL) for cost-sensitive designs.

–CoWoS-L: Hybrid silicon + RDL for larger packages (up to 12 HBM stacks) .

•PCB Impact: Requires ultra-low-loss substrates (e.g., Megtron 8) and 28+ layers for signal integrity .

2.2 CoPoS: The Panel-Scale Evolution

•Structure: Replaces silicon interposer with panel-scale RDL (600×600 mm+) → ABF substrate → PCB .

•Advantages:

–95%+ panel utilization (vs. 85% in CoWoS) .

–20–30% lower cost per unit area .

–Supports 10–12 HBM4 stacks (19 TB/s bandwidth) for AI servers .

•PCB Impact: Demands large-format HDI boards with laser-drilled microvias and glass-core substrates (e.g., for thermal stability) .

2.3 CoWoP: The Disruptive Contender

•Structure: Silicon interposer → Directly bonded to PCB (no ABF substrate) .

•Advantages:

–40–50% lower cost (ABF substrate eliminated) .

–Shorter signal paths for higher-speed interfaces (e.g., PCIe 6.0).

–Enhanced thermal management (direct heat-spreader contact) .

•PCB Impact: Relies on mSAP (modified Semi-Additive Process) PCBs with ≤25 μm line/space, void-free via fills, and ultra-low CTE materials .

3. Technical Comparison: Performance vs. Practicality

| Parameter | CoWoS | CoPoS | CoWoP |

| Line/Space | ≤5 μm (ABF) | 10–15 μm (Panel RDL) | 20–30 μm (PCB) |

| Max Size | 120×150 mm (mask limit) | 600×600 mm | Board-dependent |

| HBM Support | 6–8 stacks | 10–12 stacks (HBM4) | 6–8 stacks |

| Thermal Efficiency | Moderate | High (glass core) | Excellent (direct cooling) |

| Cost Drivers | High (silicon interposer + ABF) | Medium (panel scaling) | Low (no ABF) |

4. Key Challenges & PCB Opportunities

4.1 CoWoP: The High-Risk, High-Reward Path

•Barriers:

–PCB line/space precision lags behind ABF (25 μm vs. ≤10 μm) .

–CTE mismatch risks at chip-PCB interface .

–Limited ecosystem (only Apple’s SLP PCBs approach requirements) .

•PCB Opportunities:

–Materials: Low-CTE glass cloth (e.g., Nittobo NE-glass), peelable copper foil (e.g., Fang Bang), cationic resins .

–Processes: mSAP for fine traces, POFV (Plating Over Filled Via) for via-in-pad .

4.2 CoPoS: The Scalability Play

•PCB Requirements:

–Large-panel compatibility (310×310 mm to 700×700 mm).

–TGV (Through-Glass-Via) ready substrates for RDL integration .

•Market Timeline: 2026–2027 pilot lines (TSMC), 2028 mass production .

4.3 CoWoS: The Present Standard

•PCB Focus:

–Impedance control (±3%) for 56+ Gbps signals.

–40+ layer boards with hybrid FR-4/high-speed stacks .

5. Strategic Implications for PCB Manufacturers

5.1 Material Innovation

•CoWoP: Conductive pastes + low-CTE laminates to manage thermal stress.

•CoPoS: Glass-core substrates + halogen-free resins for panel-scale reliability .

5.2 Process Advancements

•mSAP Dominance: Critical for ≤25 μm traces in CoWoP/CoPoS .

•Laser Drilling: Aspect ratios >15:1 for stacked microvias in HDI designs .

5.3 Market Positioning

•Short Term (2025–2026): Support CoWoS-L with 18–46-layer HDI PCBs.

•Mid Term (2027–2028): Partner with OSATs for CoPoS panel-ready substrates.

•Long Term (2029+): CoWoP-ready lines for edge/AI accelerators if tech matures .

6. Conclusion: Coexistence Over Replacement

While CoPoS and CoWoP promise revolutionary cost/performance gains, CoWoS remains the near-term backbone for AI chips (e.g., NVIDIA Rubin). PCB manufacturers should:

– Prioritize HDI/mSAP: For CoWoP’s 25 μm precision demands.

– Invest in Panel-Scale Tools: To capture CoPoS’s 20–30% cost advantage.

– Monitor Glass Substrates: A game-changer for both CoPoS and FOPLP .

The winner will be PCB players who master material-process co-optimization—not just chasing the latest acronym.

Partner with SysPCB for future-proof PCBs—from 78-layer HDI for CoWoS to mSAP-ready boards for CoWoP. Contact us to co-design your advanced packaging solution.