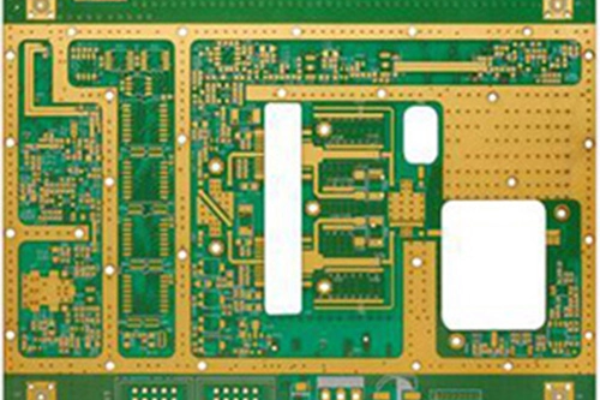

Authoritative Guide to PCB Design: 15 Key Principles for Creating High Reliability Circuit Boards

In the era of high-speed digital and RF circuits, excellent PCB design has become a decisive factor in product performance. According to statistics, PCB failures caused by design defects account for over 68% of repair cases, with EMI exceeding standards, impedance mismatch, and thermal management failure being the three core pain points. This article combines IPC standards with cutting-edge design practices to provide engineers with a full process design framework.

Table of Contents

1、 Clear design requirements: laying the foundation for success

-Electrical performance indicators:

Pre define signal rate (such as 112G PAM4), voltage tolerance (± 5%), operating temperature (-40 ℃~125 ℃), and EMC rating (such as CISPR 32 Class B).

-Structural constraints:

Confirm installation space, connector position, and heat dissipation path to avoid mechanical conflicts in the later stage.

-Design documentation:

Use standardized design requirement matrix tables (including impedance values, stacked structures, etc.) to reduce communication errors.

2、 Material selection and stacking planning: the cornerstone of electrical performance

High frequency material selection matrix

| Application scenarios | Recommended sheet materials | Key parameters |

| 5G base station (28GHz) | Rogers 4350B | Df=0.0037, εᵣ=3.48 ± 0.05 |

| Automotive Electronics | Isola IS680 | Tg=220 ℃, resistant to 150 ℃ thermal cycle |

| Consumer Electronics | Shengyi S1165 | Halogen free, with a cost of only 1.2 times that of FR-4 |

3、The golden rule of stacked design

-Recommended structure for 6-layer board:

`L1: Signal → L2: GND → L3: Signal → L4: Power → L5: GND → L6: Signal`

-Key rules:

The high-speed signal layer must be adjacent to the complete ground plane, and the routing of adjacent signal layers must be orthogonal.

4、 Signal integrity core control point

1. Impedance control practical formula

-Calculation of microstrip line impedance:

Z₀ = 87/√(εᵣ+1.41) × ln(5.98H/(0.8W+T))

(H: dielectric thickness, W: line width, T: copper thickness)

-Tolerance control:

High speed differential pair (such as USB 3.0) requires ± 5% and RF line ± 2%.

2. EMI and crosstalk suppression

-3W principle: Line spacing ≥ 3 times line width (e.g. 0.6mm spacing is required for 0.2mm line width)

-Ground shielding: Add grounding copper tape on both sides of the clock line, with a via spacing of ≤ λ/20 (≤ 15mm at 1GHz)

-Cross segmentation repair: Wiring that crosses power segmentation needs to be laid with a return ground plane on adjacent layers.

5、 Thermal management and power integrity

1. Thermal design specifications

-Copper thickness selection:

The power layer uses 2oz copper foil, which increases the current carrying capacity to 3A/mm (1oz is only 1.5A/mm).

-Heat dissipation via array:

Deploying 9 × 9 matrix vias (aperture 0.3mm/spacing 0.6mm) below BGA reduces thermal resistance by 40%.

2. Power system optimization

-Plane segmentation strategy:

Digital/analog power supplies should be isolated with a 20mil gap to avoid cross regional wiring.

-Decoupling capacitor layout:

-100nF ceramic capacitor with a distance of ≤ 2mm from the IC power pin

-Place a 10 μ F tantalum capacitor at the power inlet.

6、 DFM/DFT Collaborative Design

1. Design for Manufacturability (DFM)

-Solder pad to aperture ratio:

Through-hole pad diameter ≥ aperture+8mil (to avoid damage)

-Component spacing:

The distance between wave soldering devices should be ≥ 1.27mm, and a 3mm forbidden area should be left around the QFN.

2. Design for Testability (DFT)

-Test point specifications:

Diameter ≥ 0.8mm, center to center distance ≥ 1.5mm, to avoid being obstructed by shielding covers

-Boundary scan:

Reserved JTAG interface, supporting ICT flying pin testing.

7、 Wiring rules and process details

Wiring taboos and solutions

| Problem type | Risk | Optimization plan |

| Right angle wiring | Sudden impedance change, increased EMI radiation | 45 ° oblique angle or arc angle |

| Through hole residual stub | Signal reflection (severe when>10GHz) | Backdrilled residual stub ≤ 10mil |

| Long distance parallel wiring | 30% increase in crosstalk | 3W spacing+insertion of ground shielding wire |

8 、Advanced techniques for through-hole design

-High density BGA area:

Using laser micro holes (0.1mm aperture) combined with hole filling electroplating

-Current carrying capacity:

The through-hole with an outer diameter of 0.3mm carries a current of 1A, and 4-6 power supply holes need to be connected in parallel.

9、 Component Layout and Grounding Art

-Analog/Digital Partition:

Sensitive analog circuits (such as ADCs) should be kept at least 15mm away from digital noise sources and connected at a single point on the ground plane.

-Clock circuit layout:

The crystal oscillator is tightly attached to the IC pin, and wiring is prohibited below and a grounding guard ring is added.

-Power device positioning:

MOSFET/inductor is located near the board edge, and the heat dissipation path avoids temperature sensitive components.

Design Verification and Standard Compliance

1. Customization of DRC rule library:

Import IPC-2221A+enterprise special rules (such as automotive board micro short circuit detection)

2. Simulation driven design:

-Power integrity: Target impedance Z<0.1 Ω @ 100kHz-1GHz

-Thermal simulation: Device junction temperature ≤ 80% of rated value

3. Document delivery specifications:

Generate Gerber RS-274X format files to avoid processing errors caused by layer naming errors.

—

>Case warning: A certain industrial controller exceeded the noise limit of 12dB in the mixed signal circuit due to the absence of magnetic beads at the power division point. After optimization, a unified ground plane and partition layout were adopted, which passed the EN 55032 Class A certification.

Action guide: Immediately improve design reliability

1. Construction of material warehouse:

Establish a database for sheet metal Dk/Df and associate it with impedance calculation tools

2. Template based design:

Develop HDI/high-frequency/automotive electronics specific templates to reduce repetitive errors

3. Sign off checklist:

Covering 78 key indicators of EMC/thermal/DFM (such as pad edge spacing ≥ 0.2mm)

→ [Download the High Reliability PCB Design Checklist] ()

Quick lookup table with impedance formula, stacked structure template, and DFM problem case collection.

Get your exclusive quote immediately: fill out the form or send an email directly, and we will provide you with a quote service within 24 hours. Enjoy free DFM optimization and a 10% discount on SMT patches for your first order!