Table of Contents

Why PCB Warpage Matters More Than Ever

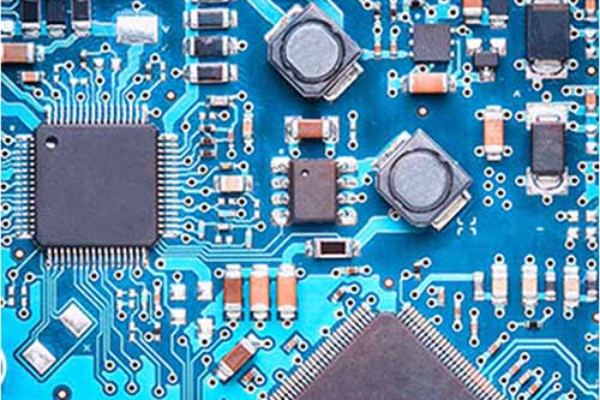

In today’s electronics landscape—where 01005 components, 0.4mm-pitch BGAs, and 16+ layer HDI boards are commonplace—PCB warpage has transitioned from a minor nuisance to a critical failure risk. Even slight curvature exceeding IPC-6012’s 0.75% threshold can cause solder joint fractures, head-in-pillow defects, or impedance mismatches. With ultra-thin boards (≤0.8mm) and lead-free reflow profiles (peaking at 260°C), managing warpage demands a holistic approach spanning materials, design, and process control.

Root Causes of PCB Warpage: A Multifaceted Challenge

1. Material-Driven Distortion

•CTE Mismatch: Glass cloth (CTE: 12–15 ppm/°C) and copper (17 ppm/°C) expand at different rates, creating shear stress at interfaces. High-Tg materials (≥170°C) reduce Z-axis expansion above Tg by ≤50 ppm/°C vs. standard FR-4’s 200–300 ppm/°C .

•Moisture Absorption: PCBs stored at >60% RH absorb moisture that vaporizes during reflow, causing “popcorn” delamination and uneven swelling .

2. Design-Induced Stress

•Copper Imbalance: When one layer’s copper coverage exceeds its opposite layer by >40%, reflow warpage risk increases by 2.8× .

•Asymmetric Stackups: 12-layer boards with unbalanced layer counts (e.g., 5-2-5) show 67% higher warpage rates than symmetric designs (e.g., 4-4-4) .

•High-Density Zones: Dense via fields under BGAs create localized stress concentrators, especially with microvias <0.2mm .

3. Manufacturing Process Failures

•Lamination Defects: Rapid heating/cooling (>2°C/min for high-Tg materials) traps residual stress. Optimal press cycles use graded ramping (1.5–2.0°C/min) and pressure staging (30–50 psi) .

•Inadequate Curing: Under-cured prepreg (<95% cross-linking) releases volatiles during soldering, causing blistering and warpage .

4. Thermal Shock in Assembly

•Reflow Stress: Thin-core boards (0.4mm) experience CTE-driven shear forces during 220–260°C temperature swings. Nitrogen reflow with ±3°C zone control reduces thermal gradients .

Warpage Mitigation: Data-Backed Solutions

A. Material Selection & Handling

Table: Warpage-Optimized Materials

| Material Type | Key Properties | Warpage Reduction | Best For |

| High-Tg FR-4 | Tg ≥170°C, Z-CTE ≤50 ppm/°C | 35% vs. standard FR-4 | Automotive, lead-free assembly |

| Modified Epoxy | X/Y CTE ≤10 ppm/°C, Dk=3.8 | 50% lower Z-expansion | 5G mmWave, server boards |

| Polyimide Flex | CTE matched to Cu (17 ppm/°C) | Eliminates Cu-film delamination | Rigid-flex, wearables |

Pre-Storage Protocol:

– Bake at 120°C for 4–6 hours if RH >60%

– Store at 23±3°C/40–60% RH in moisture-barrier bags

B. Design Rules for Flatness

1.Copper Balancing:

–Maintain <5% copper area difference between opposing layers

–Add thieving copper in sparse regions to equalize density

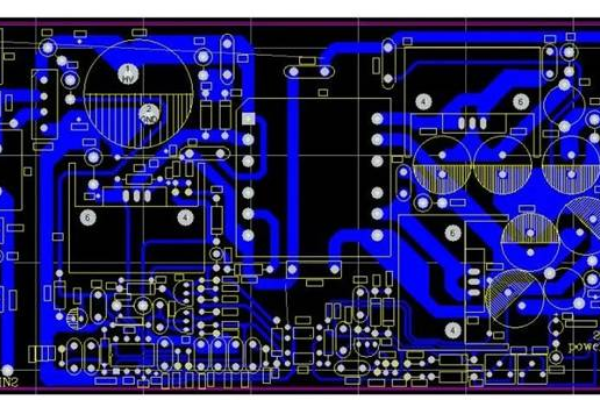

2.Symmetry Enforcement:

–Mirror layer thicknesses (e.g., L1/L12: 0.2mm, L2/L11: 0.18mm)

–Use balanced stackups (e.g., 3+6+3 vs. 5+2+5)

3.Via & Routing Optimization:

–Stagger microvias in BGA zones to avoid stress corridors

–Replace V-Cut with routed tabs to preserve edge integrity

C. Process Innovations

•Lamination Control:

- graph LR

A[Preheat 80–110°C] –> B[Resin Flow 170–185°C]

B –> C[Full Cure 190–200°C]

C –> D[Graded Cooling 2°C/min] - Achieves >99.5% interlayer bonding and near-zero residual stress

•Post-Lamination Stress Relief:

Bake boards at 120–140°C for 1–2 hours to release internal stresses

•Assembly Support:

Use synthetic stone pallets during reflow to constrain thin boards (<1.0mm)

Advanced Warpage Control Technologies

•In-Line 3D Scanning: Laser profilometers measure warpage in real-time with ±0.02mm accuracy, triggering automatic process adjustments .

•Finite Element Analysis (FEA): Simulates thermal stress distribution to predict warpage hotspots during design .

•Low-CTE Copper Foils: Reverse-treated foils with CTE <16 ppm/°C minimize Z-axis expansion mismatch .

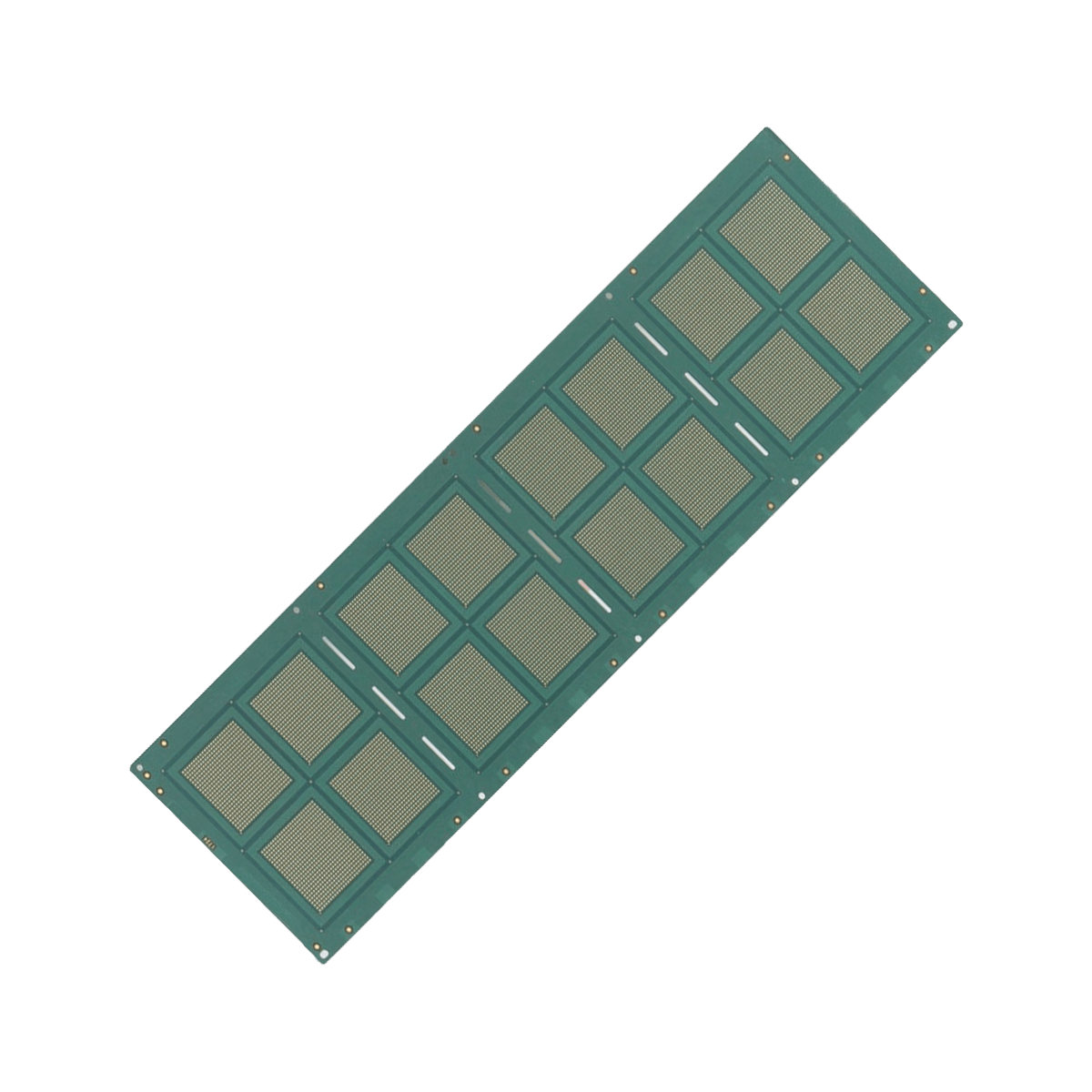

Case Study: Warpage Reduction in 14-Layer Server Boards

A leading hyperscaler achieved 0.45% warpage (vs. 1.2% industry avg.) through:

1. Switching to Tg 180°C modified epoxy with 30% silica filler

2. Implementing symmetrical 5-4-5 stackup with ±3% copper balance

3. Adopting vacuum lamination at 50 psi with 2°C/min ramp rates

4. Using ENIG surface finish (reduced thermal stress vs. HASL)

Future Frontiers: Smart Materials & AI-Driven Control

•Self-Leveling Substrates: Polymer-ceramic composites that dynamically counteract thermal stress.

•ML-Based Warpage Prediction: Training datasets from 10,000+ PCBs to forecast distortion risks during design.

“In the era of 01005 components and 20-layer HDI, warpage control transcends manufacturing—it’s a system engineering discipline. From material molecular structures to reflow thermodynamics, every variable must be orchestrated.”

Partner with Precision. Build with Confidence.

→ [Download Our Warpage Design Checklist]

→ [Request a CTE-Material Consultation]

→ [Explore In-Line Warpage Monitoring Solutions]