Table of Contents

Executive Summary

Thermal stress in printed circuit boards (PCBs) is a critical factor influencing the reliability and longevity of electronic devices. It arises from Coefficient of Thermal Expansion (CTE) mismatches between different materials within the PCB stack-up when subjected to temperature variations during manufacturing (e.g., soldering) and operational life (e.g., power cycling). This stress can lead to delamination, via barrel cracking, solder joint fatigue, and overall structural deformation. Understanding its root causes, accurately analyzing its effects through simulation and testing, and implementing robust mitigation strategies—from material selection to design optimization—are essential for producing durable PCBs, especially in high-reliability industries such as automotive, aerospace, and high-performance computing.

1. Introduction to Thermal Stress in PCBs

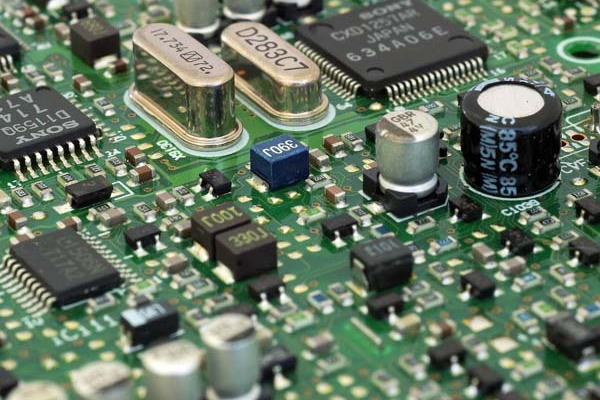

In the realm of PCB design and manufacturing, thermal stress refers to the mechanical stress induced within the board structure due to temperature changes. This phenomenon occurs because different materials constituting a PCB—such as copper conductors, FR-4 substrates, solder masks, and ceramic components—expand and contract at different rates when heated or cooled. This differential expansion, governed by their unique Coefficients of Thermal Expansion (CTE), generates internal forces that can strain or deform the board .

The increasing complexity of modern electronics, characterized by multilayer boards, high-density interconnects (HDI), and the use of lead-free solders requiring higher reflow temperatures, has amplified the challenges associated with thermal stress. Effectively managing this stress is not merely a design consideration but a fundamental requirement for ensuring product reliability, particularly in applications exposed to extreme environments or frequent thermal cycling .

2. Fundamental Causes of Thermal Stress

2.1 Coefficient of Thermal Expansion (CTE) Mismatch

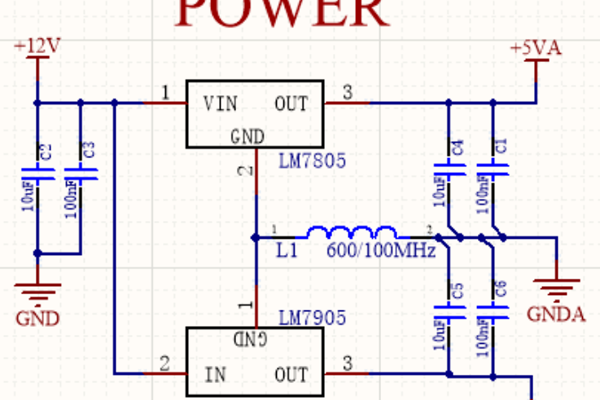

The primary driver of thermal stress is the mismatch in CTE between the various materials bonded together in a PCB.

•Material CTE Disparity: The copper used in traces and planes has a CTE of approximately 17-18 ppm/°C. In contrast, the common FR-4 substrate, which is a composite of glass fiber and epoxy resin, exhibits a CTE in the range of 12-18 ppm/°C in the X-Y plane (in-plane), but a significantly higher 50-60 ppm/°C in the Z-axis (through-thickness) . When the board undergoes temperature changes, this disparity, especially the high Z-axis CTE, creates shear stresses at the copper-substrate interface and within plated through-holes (PTHs).

•Component Interactions: Semiconductor materials like silicon have a very low CTE (~3 ppm/°C). When mounted on a PCB with a higher CTE, the solder joints (e.g., SAC305 with CTE ~24 ppm/°C) bear the brunt of the CTE mismatch during temperature cycles, leading to cyclic shear stress and eventual fatigue failure .

2.2 Temperature Fluctuations in Manufacturing and Operation

PCBs are subjected to multiple thermal excursions throughout their lifecycle:

•Manufacturing Processes: Key stages like soldering reflow (with peak temperatures up to 260°C for lead-free processes), hot air solder leveling, and conformal coating curing involve rapid and significant heating and cooling. These “thermal shocks” can lock in residual stresses if not properly managed .

•Operational Power Cycling: During use, electronic components power on and off, generating heat and causing localized expansion. The resulting temperature gradients across the board create non-uniform stress distributions.

2.3 Constrained Expansion

When a PCB is mounted inside an enclosure or chassis using screws or brackets, its natural ability to expand and contract with temperature is mechanically constrained. This external constraint can force the board to bow or warp, generating significant bending stresses, particularly in larger boards .

3. Key Impacts and Failure Mechanisms

Unmanaged thermal stress manifests in several critical failure modes that compromise PCB functionality and lifespan.

3.1 Plated Through-Hole (PTH) and Via Failures

The Z-axis CTE mismatch is most severe for vertical interconnects. The copper plating in a PTH or via (CTE ~17 ppm/°C) is constrained by the surrounding substrate expanding much more in the Z-direction (CTE ~55 ppm/°C). During thermal cycles, this generates repeated tensile and compressive stresses on the copper barrel, leading to:

* Barrel Cracking: Cyclic stress fatigues the copper, initiating micro-cracks that can propagate, leading to open circuits .

* Pad Lifting: The copper pad at the end of a via can separate from the underlying substrate material due to high peeling (normal) stress.

3.2 Solder Joint Fatigue

Solder joints are the weakest link in managing CTE mismatch between a component and the PCB. The differential expansion and contraction during temperature cycling impose a shear strain on the solder balls (e.g., in BGAs) or leads (e.g., in QFPs). This leads to:

* Crack Initiation and Propagation: Repeated strain cycles cause work hardening and micro-cracking within the solder material, increasing electrical resistance and eventually causing intermittent or complete failure .

* Strain Concentration: The corners of large components experience the highest displacement, making their solder joints the most susceptible to fatigue failure.

3.3 Delamination and Warping

•Delamination: High Z-axis expansion can exceed the bond strength between PCB layers, causing separation. This is exacerbated if moisture is present, which can turn to steam during high-temperature assembly .

•Warping and Bow: Non-uniform material distribution or asymmetric stack-up can cause the entire board to warp when heated. This deformation can misalign components, strain solder joints, and even prevent proper assembly into a chassis .

4. Analyzing and Predicting Thermal Stress

Proactively identifying and quantifying thermal stress is crucial for high-reliability designs.

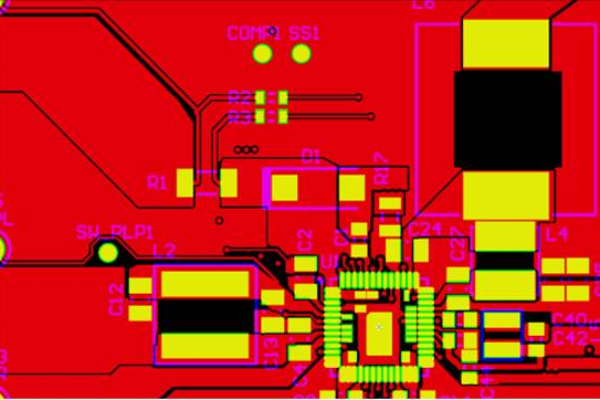

4.1 Simulation and Finite Element Analysis (FEA)

Software tools like ANSYS are widely used for thermal stress simulation. The process typically involves:

* Transient Thermal Analysis: First, the temperature distribution across the PCB under specific thermal loads is calculated .

* Structural Analysis: The resulting temperature field is then applied to a structural model to compute the induced stresses, strains, and deformations .

* Identifying Critical Areas: FEA pinpoints high-stress regions, such as the corners of BGA solder balls or the barrel of vias, allowing designers to focus mitigation efforts .

4.2 Physical Testing and Standards

Simulations are validated and supplemented by physical tests that subject PCBs to controlled thermal stress.

* Temperature Cycling Test (TCT): The board is repeatedly cycled between high and low-temperature extremes in a chamber. The number of cycles a board withstands before failure is a key reliability metric. Standards like IPC-TM-650, JESD22-A104, and MIL-STD-883 define the test parameters for different application grades .

* Interconnect Stress Test (IST): This test accelerates failure in plated through-holes by rapidly cycling current through dedicated daisy-chain networks, heating them internally and measuring resistance changes to detect failures .

* Standardized Monitoring: The Chinese national standard GB/T 45723-2025 provides a specific method for monitoring the resistance change of a single plated-through-hole during temperature cycling to assess its durability .

5. Material Selection to Mitigate Thermal Stress

Choosing the right materials is the first line of defense against thermal stress failures.

•High-Tg (Glass Transition Temperature) Materials: When the operating temperature exceeds a material’s Tg, its CTE increases dramatically, and its mechanical properties degrade. Using high-Tg FR-4 (Tg > 170°C) or more advanced substrates like polyimide (Tg > 250°C) maintains dimensional stability at higher assembly and operating temperatures .

•Low-CTE and Engineered Materials: For demanding applications, materials with tailored CTE are available.

–Ceramic-filled Laminates: These materials can reduce the Z-axis CTE to 30-40 ppm/°C, significantly lowering the stress on PTHs and vias.

–Modified Epoxy Systems: Halogen-free and low-loss materials often incorporate fillers that help moderate the CTE.

•Emerging Sustainable Materials: Research into eco-friendly alternatives shows promise. Studies on Lignocellulose Nanofibrils (LCNF) derived from wood pulp indicate potential for sustainable PCB substrates with competitive mechanical and thermal properties .

Table: Comparison of PCB Substrate Material Properties

| Material Type | Typical X-Y CTE (ppm/°C) | Typical Z-CTE (ppm/°C) | Tg (°C) | Key Characteristics |

| Standard FR-4 | 14-18 | 55-60 | 130-140 | Cost-effective, general purpose |

| High-Tg FR-4 | 12-15 | 45-50 | 170-180 | Better stability for lead-free assembly |

| Polyimide | 12-15 | 45-55 | 250-260 | Excellent high-temp and chemical resistance |

| Rogers 4350B | 12-15 | 40-50 | >280 | Low loss, for high-frequency circuits |

| LCNF (Experimental) | Data under research | Data under research | Data under research | Sustainable, wood-derived |

6. Design Strategies to Minimize Thermal Stress

Smart design practices can effectively redistribute and reduce thermal stress.

•Balanced and Symmetric Stack-up: A symmetric arrangement of copper layers and prepreg (pre-impregnated) layers around the central plane of the board balances the inherent stresses, minimizing warpage. For example, an 8-layer board should have a mirror-image stack-up on either side of the core .

•Via and PTH Design Optimization:

–Adequate Annular Ring: Ensure sufficient copper pad size around via holes to resist pad lifting.

–Teardrop Transitions: Use teardrop-shaped connections where traces meet pads or vias to reduce stress concentration points.

–Via-in-Pad Filling: Filling vias with conductive or non-conductive epoxy before placing a pad on top provides a flat surface and reinforces the structure.

•Copper Balancing: Distributing copper as evenly as possible across each signal layer prevents localized areas with different thermal masses and expansion rates, which can lead to warping.

•Solder Joint Relief: For components with known large CTE mismatches, using softer, more compliant underfill materials can absorb some of the shear strain, dramatically extending the fatigue life of solder joints.

7. Conclusion: A Proactive Approach to Reliability

Thermal stress in PCB substrates is an inescapable physical reality in electronic product development. However, its detrimental effects on product reliability are not inevitable. By developing a fundamental understanding of its causes, primarily CTE mismatch, and recognizing its potential failure mechanisms, such as PTH cracking and solder fatigue, designers and engineers can take proactive control.

A comprehensive strategy that integrates careful material selection, thermal-aware design principles, and advanced simulation and testing methodologies is key to building robust and reliable PCBs. As electronics continue to push the boundaries of power, density, and operating environments, mastering the management of thermal stress will remain a critical differentiator for leading PCB manufacturers and the brands they supply.

Partner with Us for Your Reliable PCB Solutions

Navigating the complexities of PCB thermal stress requires a manufacturing partner with deep expertise and advanced capabilities. Our proficiency in material science, thermal simulation, and design for manufacturability (DFM) ensures that your boards are engineered for maximum reliability from the ground up.

Contact us today to discuss how we can help you optimize your next PCB project for performance and longevity in even the most demanding thermal environments.