Table of Contents

Executive Summary

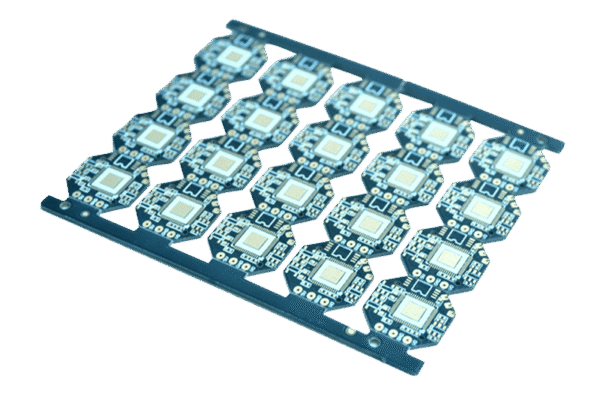

Chip soft failures in semiconductor devices represent a critical challenge in modern electronics, particularly as process technologies continue to shrink toward nanometer scales. These transient errors occur when external radiation or internal noise causes unexpected data corruption without permanent hardware damage . For PCB manufacturers and designers, understanding soft error mechanisms, their impact on system reliability, and effective mitigation strategies has become increasingly crucial—especially in applications requiring high reliability, such as aerospace systems, automotive electronics, medical devices, and data center infrastructure . This comprehensive guide explores the fundamental principles of soft errors, their underlying causes, measurement methodologies, and practical implementation strategies to enhance system resilience in PCB-based electronic systems.

1.Understanding Chip soft failures in Semiconductor Devices

1.1 What Are Chip soft failures?

Chip soft failures, also known as soft errors or transient faults, are temporary, non-destructive malfunctions in electronic systems where data becomes corrupted but the physical hardware remains undamaged . Unlike hard failures that result from permanent physical damage, soft errors are reversible conditions that can be corrected by rewriting the correct data or resetting the system . In computer memory systems, soft errors may alter a single bit (single-bit upset) or multiple adjacent bits (multi-bit upset), potentially causing program execution errors or data corruption without damaging the underlying semiconductor structure .

The fundamental characteristic that distinguishes soft errors from other failure types is their transient nature. Once the erroneous data is overwritten with correct values or the system is rebooted, the hardware returns to normal operation without permanent damage . This temporary aspect makes soft errors particularly challenging to diagnose and address, as they may occur randomly and not leave tangible evidence of their occurrence after the fact.

1.2 Historical Context and Growing Significance

The semiconductor industry began recognizing soft errors as a significant reliability concern in the 1970s when DRAM devices started exhibiting random errors that couldn’t be attributed to permanent hardware defects . As process technologies have advanced from micrometer to nanometer scales, the problem has intensified dramatically due to several converging factors:

•Reduced Node Sizes: As transistor dimensions shrink from 0.24μm to 90nm and below, the critical charge (QCRIT) required to maintain data stability in memory cells has decreased significantly . This reduction makes modern semiconductor devices more susceptible to disturbance from lower-energy particles.

•Lower Operating Voltages: The progressive reduction of supply voltages from 5V to 3.3V, 1.8V, and now below 1V in advanced nodes means noise margins have substantially decreased, making circuits more vulnerable to soft errors .

•Increased Circuit Density: Higher integration densities mean more memory cells and logic elements are packed into smaller areas, increasing the probability that a radiation event will affect sensitive components .

These technological trends have transformed soft errors from a niche concern affecting only specialized applications to a mainstream reliability challenge that impacts consumer electronics, enterprise systems, and critical infrastructure .

2.Fundamental Mechanisms Behind Soft Errors

2.1 Radiation-Induced Soft Errors

The primary cause of soft errors in semiconductor devices is radiation interaction with silicon substrates. There are three major radiation mechanisms responsible for most soft errors:

2.1.1 Alpha (α) Particle Radiation

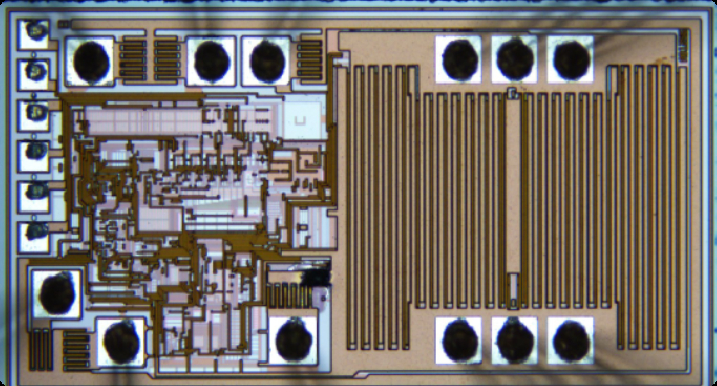

Alpha particles are helium nuclei (two protons and two neutrons) emitted during the decay of radioactive impurities such as Thorium-232 and Uranium-238 present in packaging materials . These particles typically possess energies between 2-9 MeV and can generate significant electron-hole pairs as they pass through silicon—approximately 1 million electron-hole pairs for a single alpha particle, given that only 3.6 eV is required to create one pair in silicon .

When these generated charges collect in depletion regions of reverse-biased transistors, they can create current disturbances sufficient to flip the state of memory cells if the collected charge exceeds the cell’s critical charge (QCRIT) . The electric field in depletion regions accelerates charge drift, amplifying this effect and potentially altering stored data values from 0 to 1 or vice versa.

2.1.2 Cosmic Ray Interactions

Cosmic rays from galactic sources and solar radiation interact with Earth’s atmosphere to produce high-energy neutrons and protons that can reach ground level . Unlike alpha particles, neutrons carry no electrical charge, enabling them to penetrate deeply through materials—they can pass through several feet of concrete and easily traverse typical electronic enclosures .

The interaction mechanism differs significantly from alpha particles: neutrons primarily cause soft errors through nuclear collisions with silicon atoms . When a high-energy neutron (typically 100-800 MeV) strikes a silicon nucleus, it creates a cascade of secondary particles through nuclear spallation reactions, generating dense tracks of electron-hole pairs that can disrupt multiple memory cells simultaneously .

Table: Comparison of Radiation-Induced Soft Error Mechanisms

| Parameter | Alpha Particles | Cosmic Ray Neutrons |

| Source | Radioactive impurities in packaging materials | Cosmic ray interactions with atmosphere |

| Energy Range | 2-9 MeV | 100-800 MeV |

| Interaction Mechanism | Direct ionization | Nuclear collisions with silicon atoms |

| Penetration Depth | Low (micrometers) | High (feet of concrete) |

| Geographic Variation | Minimal | 3x at high altitude vs. sea level |

| Mitigation Approach | High-purity materials | Circuit hardening, error correction |

2.1.3 Thermal Neutron Effects

Thermal neutrons with much lower energies (approximately 25 meV) can also cause soft errors through interaction with Boron-10 isotopes present in BPSG (Boron Phosphosilicate Glass) dielectric layers . When Boron-10 captures a thermal neutron, the resulting nuclear fission produces lithium ions and alpha particles that can subsequently generate electron-hole pairs and potentially cause soft errors . This mechanism can be completely eliminated by using boron-free materials or enriching boron with Boron-11 isotope .

2.2 Environmental and Operational Factors

The rate at which soft errors occur varies significantly based on environmental conditions and operational parameters:

•Altitude Effects: At commercial airline altitudes (35,000 feet), the neutron flux can be 100-800 times higher than at sea level, dramatically increasing soft error rates in avionics systems .

•Geographic Location: The intensity of cosmic ray-induced neutrons varies with latitude and longitude, with locations like London experiencing approximately 1.2 times the neutron flux of equatorial regions .

•Circuit Sensitivity: Memory cells with lower critical charge (QCRIT) are more susceptible to soft errors. As process technologies advance and operating voltages decrease, QCRIT values diminish, making modern nanoscale circuits increasingly vulnerable .

3.Measuring and Quantifying Soft Error Rates

3.1 Standardized Metrics and Units

The semiconductor industry employs standardized metrics to quantify and compare soft error susceptibility across different technologies and applications:

•FIT Rate: Failures in Time (FIT) is defined as the number of failures per billion device-hours of operation . A rate of 1,000 FIT corresponds to a Mean Time To Failure (MTTF) of approximately 114 years for a single device .

•FIT-per-Mbit: For memory devices, the soft error rate is often normalized per megabit to facilitate comparison between different memory densities .

These standardized metrics enable designers to make informed decisions about component selection and implementation of error mitigation techniques based on system reliability requirements.

3.2 Accelerated Testing Methodologies

Due to the random nature of soft errors and their typically low occurrence rates under normal conditions, manufacturers employ accelerated testing techniques to estimate real-world performance in practical timeframes:

•Alpha Particle Acceleration: Testing involves placing radioactive materials such as thorium or uranium directly on decapped chips to measure their sensitivity to alpha particle radiation .

•Neutron Acceleration: Specialized facilities like Los Alamos National Laboratory provide controlled neutron beams that simulate cosmic ray effects, enabling rapid assessment of device susceptibility to neutron-induced soft errors .

•System-Level Testing: Thousands of devices are deployed in field environments while monitoring for errors, providing real-world soft error rate data, though this approach is time-consuming and expensive .

These accelerated testing methods typically produce conservative estimates (upper bounds) of soft error rates, helping ensure adequate safety margins in reliability-critical applications .

4.Impact on Electronic Systems and Applications

4.1 System-Level Consequences

The impact of soft errors varies dramatically across different electronic systems and applications:

•Consumer Electronics: For applications such as mobile phones with 4Mbit low-power memory exhibiting 1,000 FIT-per-Mbit, soft errors might occur only once every 28 years, making them relatively insignificant for most consumer applications .

•Network Infrastructure: High-end routers incorporating 10Gbit of SRAM memory with 600 FIT-per-Mbit would experience errors approximately every 17 hours on average, necessitating robust error mitigation strategies .

•Avionics and High-Altitude Systems: The combination of high memory density and increased neutron flux at altitude creates particularly challenging environments. A laptop with 2Gbits of memory operating at 35,000 feet could experience soft errors approximately every 5 hours due to significantly elevated FIT rates .

4.2 Application-Specific Considerations

The appropriate level of soft error protection depends heavily on the target application and its reliability requirements:

•Non-Critical Systems: Applications processing pre-compressed audio, video, or static imagery may tolerate soft errors with minimal impact on user experience, as isolated bad bits in capture or playback buffers may be imperceptible to users .

•Mission-Critical Systems: Applications controlling system operations or managing critical data require robust soft error mitigation, as single bit flips could cause functional failures, system crashes, or catastrophic outcomes in safety-critical applications .

•High-Reliability Computing: Enterprise servers, data center infrastructure, and telecommunications equipment typically implement comprehensive soft error protection to maintain data integrity and system availability despite employing large amounts of memory .

5.Mitigation Strategies for PCB Designers

5.1 System-Level Mitigation Techniques

PCB designers and system architects can implement several strategies to mitigate soft error impacts:

5.1.1 Error Detection and Correction Codes

Error Correcting Codes (ECC) provide one of the most effective approaches for mitigating soft errors in memory subsystems . These codes add redundant bits to stored data, enabling the detection and correction of single-bit errors and detection of multi-bit errors:

•Implementation Overhead: ECC typically increases chip size by at least 20% due to the additional circuitry required for encoding and decoding .

•Performance Impact: Error detection and correction introduce additional latency during memory read operations, though this is often acceptable in reliability-critical applications .

•Effectiveness: Properly implemented ECC can effectively correct all single-bit errors within a protected word, significantly improving system reliability .

5.1.2 Architectural Enhancements

System architecture decisions can significantly influence soft error resilience:

•Memory Topology: Strategic arrangement of memory bit maps can help confine physical multi-bit events to single bytes, limiting error propagation .

•Redundant Processing: Techniques such as triple modular redundancy (TMR) and algorithm-based fault tolerance (ABFT) provide protection for processing elements .

•Selective Hardening: Identifying and specifically hardening the most vulnerable circuit portions optimizes the trade-off between reliability and implementation cost .

5.2 Circuit-Level Mitigation Techniques

At the circuit design level, several approaches can enhance soft error resilience:

•Increased Critical Charge: Designing memory cells with higher critical charge (QCRIT) values improves their inherent resistance to soft errors, though this may conflict with power and performance objectives .

•PMOS Transistor Optimization: Adjusting PMOS threshold voltages can shorten cell recovery time, indirectly enhancing soft error immunity .

•Triple-Well Structures: Implementing buried junctions such as triple-well structures creates a counter-acting electric field in NMOS depletion regions that pulls generated charges away from active areas .

•Selective Hardening: Identifying nodes with high soft error susceptibility and specifically hardening them using specialized circuit techniques optimizes the area-reliability trade-off .

5.3 Manufacturing and Material Considerations

Material selection and manufacturing processes significantly impact device susceptibility to soft errors:

•High-Purity Materials: Using packaging materials with minimal radioactive impurities reduces alpha particle emissions, directly decreasing soft error rates .

•Boron-Free Dielectrics: Eliminating Boron-10 from BPSG dielectric layers prevents thermal neutron-induced soft errors .

•Process Optimization: Manufacturing processes can be tuned to enhance charge collection characteristics and reduce soft error susceptibility .

6.Future Trends and Emerging Challenges

6.1 Technology Scaling Implications

As semiconductor technology continues to advance, several concerning trends threaten to exacerbate soft error challenges:

•Decreasing Critical Charge: Each new technology generation typically reduces the critical charge required to flip memory states, increasing susceptibility to lower-energy radiation events .

•Voltage Scaling: Progressive reduction of operating voltages shrinks noise margins, making circuits more vulnerable to transient disturbances .

•Increased Circuit Density: Higher integration densities mean more potential targets for radiation-induced errors within the same chip area .

These trends suggest that soft errors will remain a significant reliability challenge for the foreseeable future, requiring ongoing research and innovation in mitigation techniques.

6.2 Emerging Mitigation Approaches

Research institutions and semiconductor companies are developing new approaches to address soft error challenges in advanced nodes:

•Selective Hardening Methodologies: Techniques that identify and specifically protect the most vulnerable circuit portions enable more efficient resource utilization .

•Built-In Self-Test and Recovery: Integrating self-test capabilities with automatic recovery mechanisms enhances system resilience while minimizing performance impacts .

•Algorithmic Fault Tolerance: Developing computation algorithms with inherent error detection and correction capabilities provides software-level protection against hardware soft errors .

These emerging approaches, combined with traditional mitigation techniques, will help ensure continued system reliability despite increasingly challenging soft error environments.

7.Conclusion

Chip soft failures represent a significant and growing challenge in modern electronic systems, particularly as semiconductor technologies continue scaling toward smaller nodes with reduced noise margins and lower operating voltages. For PCB designers and system architects, understanding soft error mechanisms, measurement methodologies, and mitigation strategies is essential for developing reliable systems—especially for applications deployed in high-radiation environments or requiring exceptional operational reliability.

A comprehensive approach to soft error mitigation typically combines multiple strategies, including careful material selection, circuit hardening techniques, architectural redundancy, and system-level error detection and correction. The optimal combination of these approaches depends on specific application requirements, cost constraints, and reliability targets.

As technology continues advancing, soft error mitigation will remain an active area of research and development, requiring ongoing attention from PCB manufacturers and system designers to ensure the continued reliability of electronic systems in increasingly challenging operational environments.

Partner with Us for Your Reliability-Critical PCB Designs

Successfully implementing robust soft error mitigation requires expertise in both PCB design and system architecture. Our specialized capabilities in high-reliability PCB manufacturing, signal integrity optimization, and thermal management ensure that your designs meet stringent reliability requirements for aerospace, automotive, medical, and enterprise applications.

Contact us today to discuss how we can support your next reliability-critical project with PCB solutions that deliver optimal performance and resilience against soft errors and other reliability challenges.