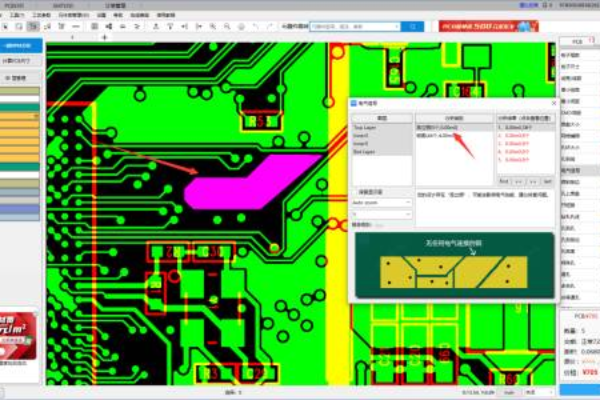

In PCB design, providing a stable voltage to signals and proper voltage distribution are two basic goals in power system design. With the emergence of signal integrity problems, reflection, crosstalk, etc. will affect the stability of the power supply system, coupled with the continuous reduction of the chip operating voltage, the fluctuation of the power supply will affect the normal operation of the system. Power integrity analysis is to ensure a stable and reliable power supply in the PCB.

Power Integrity Analysis Overview

Power integrity refers to the quality of the power waveform in a system. With the improvement of the output switching speed of the IC, the edge rate of the signal, that is, the time for the signal to rise and fall, is rapidly reduced, and the power line suffers a large voltage drop due to its parasitic inductance. For the signal edge rate less than 1ns, the voltage between the power supply layer and the ground layer on the PCB will be different everywhere on the circuit board, which will affect the stability of the power supply of the chip, and even cause the logic error of the chip

Factors that cause power system instability:

synchronous switching noise,

non-ideal power supply impedance effects,

resonance, and edge effects.

In general, synchronous switching noise is the main source of power supply noise. Due to the parasitic inductance of the ground lead and the plane, a certain voltage fluctuation will be caused under the action of the switching current, that is to say, the reference ground of the device is no longer zero level. Therefore, the ground level to be sent by the driver will appear corresponding interference waveform, and the phase of the interference waveform is the same as that of the ground noise. For the switching signal waveform, the influence of the ground noise will cause the falling edge of the signal to slow down; at the receiving end, the signal waveform will also be disturbed by the ground noise. But the phase of the interference waveform is opposite to the ground noise. In addition, in some memory components, there may be accidental inversion of data due to power supply noise and ground noise.

In high-frequency circuits, there are a lot of parasitic parameters in the power plane. These parasitic parameters can be regarded as an LC resonant network composed of many inductances and capacitors, or a resonant cavity. At a certain frequency, these capacitors and inductors will resonate, thereby affecting the impedance of the power plane. In addition to the resonance effect, the edge effect of the power plane and the ground plane is also a problem that needs to be paid attention to in the power supply design. The edge effect here refers to the phenomenon of edge reflection and radiation. The size of the copper clad surface on the edge of the circuit board is limited, so it is prone to electromagnetic interference problems. Decoupling capacitors are usually added in engineering to reduce the radiation effect of the edge and achieve the purpose of suppressing power plane noise.

Synchronous switching noise

Synchronous switching noise (SSN) is primarily generated by the synchronous switching output accompanying the device. The faster the switching speed, the more significant the instantaneous current change, and the greater the inductance on the current loop, the more serious the synchronous switching noise generated. It can be seen that the magnitude of synchronous switching noise depends on the I/O characteristics of the integrated circuit, the impedance of the power plane and ground plane of the PCB board, and the layout and routing of high-speed devices on the PCB.

Depending on the return path, synchronous switching noise can be divided into off-chip switching noise and on-chip switching noise. Off-chip switching noise refers to the noise generated when the current caused by the signal switch flows back through the signal line and the power supply/ground plane; if the switch state changes, the current return path passes through the power supply and ground instead of the signal line, and the noise at this time is On-chip switching noise.

Reduction of switching noise in the chip

Mainly achieved by reducing the inductance of the path through which the switching signal flows or slowing down the rate of change of the switching signal to reduce the induced voltage. The off-chip switching noise can be reduced by reducing the switching rate and the number of simultaneous switches of the on-chip drivers, and using the chip with the slowest edge rate that can meet the timing requirements; or by reducing the package loop inductance and increasing the coupling inductance between the signal and power and ground; A bypass capacitor can also be used inside the package to allow the power supply and ground to share the current loop and reduce the equivalent inductance of the return path.

Power Distribution Design

Power supply noise largely originates from a non-ideal power distribution system. The power distribution system is to provide enough power to all the devices in the system. These devices not only need sufficient power loss, but also have certain requirements on the stability of the power supply. Because there is always an impedance in the actual power plane, when there is an instantaneous current passing through, a voltage drop will be generated, which will lead to fluctuations in the power supply. Most devices require power supply fluctuations within 5% of normal voltage.

To ensure proper operation of each device, the impedance of the power plane should be reduced as much as possible. When the operating frequency is relatively high, it is necessary to calculate both the DC impedance of the resistor and the AC impedance caused by the inductance. When controlling the impedance of the power supply, the internal resistance of the power supply can be reduced by using materials with low resistivity, short and thick power lines, the power supply as close to the ground as possible, and the use of decoupling capacitors to reduce the resistance and inductance of the power supply, thereby reducing the source impedance.